I’m old enough to remember the “good old days” of when radios and RF technology were almost exclusively designed in analog hardware. Circuits were designed to achieve specific analog tuning and different frequencies or modulation schemes required adding new components by hand, often to complicated circuits that required deep knowledge from amateur radio enthusiasts or electrical engineers.

The development and eventual mainstreaming of the FPGA was the asteroid that heralded the end of the dinosaurs for analog radio in many applications. Developed in the 90’s and popularized in the early 2000’s, the “Field programmable Gate Array” or FPGA was a marvel of technology which allowed performing complex algorithms without the need for conventional processor instructions. FPGAs used a large series of logic gates, or “nets” which could be programmed into arbitrary configurations. Algorithms could be coded into the configuration of these gates, allowing signal processing and DSP to be performed with lightning-fast performance and near-perfect determinism. FPGAs were not as flexible to code as conventional x86 processors and microcontrollers, but once an algorithm was developed it was often orders of magnitude faster than the soft real-time performance of conventional processing hardware such as CPUs and GPUs. Signal processing also required significantly lower power utilization as the only requirement was to keep logic gates energized in their current configuration; there was no clock rate driving instructions to be performed and no need to continuously adjust transistors through repetitive instructions.

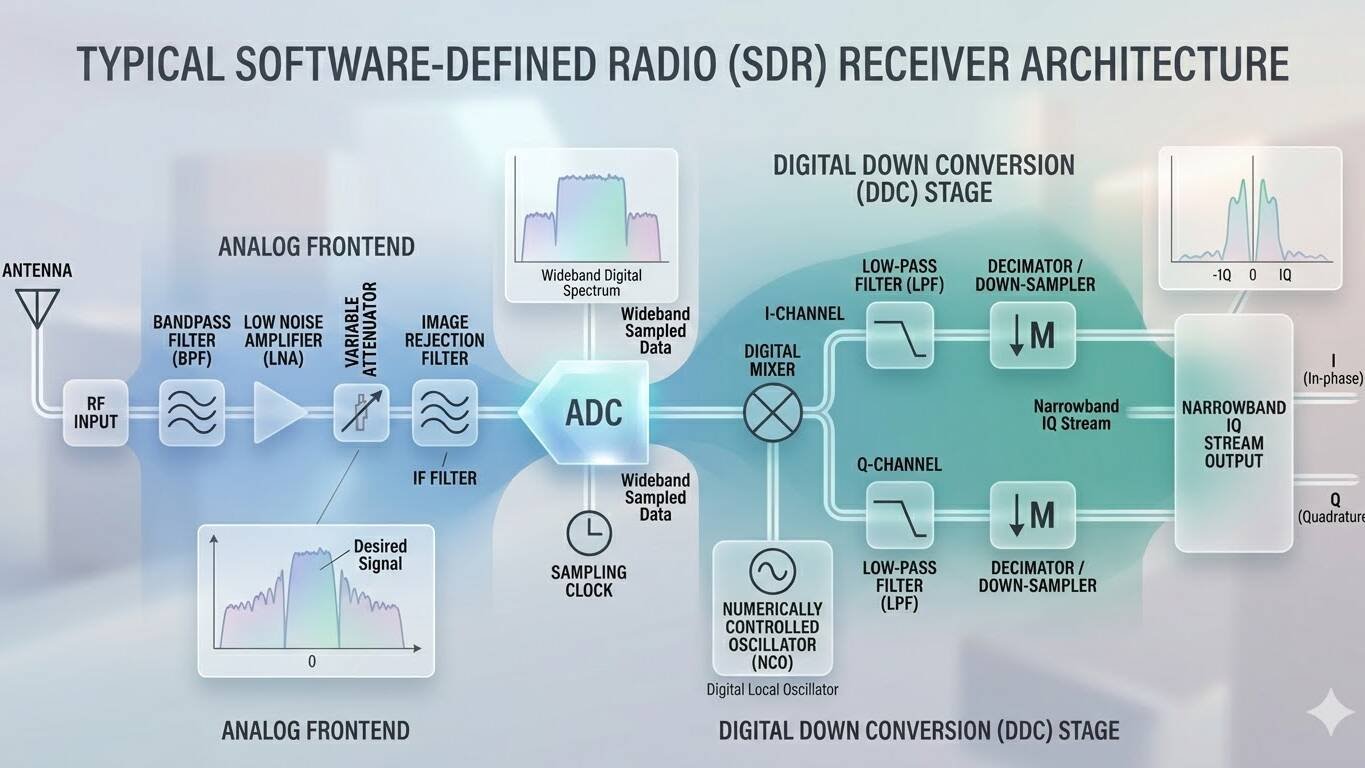

RF engineers started to tap into the potential of this technology in the 90’s, bringing it to fruition by the early 2000’s. Radios went from being devices designed to tune at a limited set of analog frequencies to what we now refer to as “software-defined,” where the behavior and performance of a device was almost entirely defined in the digital domain. Most SDRs moved towards what was referred to as a “Wide Open Frontend” (WOFE) where a bandpass filter is placed around the spectrum of interest and the entire band is sampled by a clock running at the Nyquist rate of twice the bandwidth of this desired spectrum. Once the full band was sampled, an FPGA could be used to perform digital operations on the entire spectrum depending on user requirements. A common algorithm performed in this case is down conversion, in which the wideband data is decimated through a filter and a frequency shift is applied, allowing the user to focus on narrower portions of the spectrum that contain signals of interest. The FPGA can be rapidly reprogrammed to adjust the parameters used for decimation and frequency shifting, allowing the radio to agilely move between different frequencies and present a narrow-band view of the spectrum to the user. This can be done for an arbitrary number of down conversion chains and is only limited by the amount of compute available on the FPGA. These resulting narrowband channels can then be sent as streams of IQ to conventional hosts where less intensive algorithms can be run on the decimated data.

This architecture is brilliant because it allows the radio to be flexibly defined in terms of supporting a large number of frequencies and sample rates. So long as the data is captured in the analog frontend, it can be processed and decimated in the backend to make it immediately useful to the user without needing to send data at the full clock rate of the device. It is deterministic, power-efficient, and can be tuned to the optimal bandwidth for the signals that the user desires to see. Because FPGAs can be rapidly reprogrammed, it is also suitable for telecommunications and radar systems where agility in frequency and RF configuration is important and must be performed in real-time. Other key parameters can also be digitally exposed, such as the start phase of the numerically-controlled oscillator which can be used to impart phase offsets used for beamforming on either transmit or receive.

What are the tradeoffs of this design? The most important is that using a completely wide open analog frontend allows the radio to receive noise across the entire spectrum, potentially introducing interference and also saturating the analog to digital converter with signals that may not be of interest to the user. There is a case to be made in RF design for keeping the bandpass filter on the analog frontend as small as possible so that only the region of interest is sampled and signals are rejected from anywhere that is out of band. A reasonable compromise is to introduce programmable analog filters into the front end, which allows selectively accepting and rejecting different parts of the band in the event that strong interference is present that can be preferentially rejected.

Another tradeoff is the difficulty in application design for FPGAs. These must be programmed through complex languages such as VHDL and Verilog and lack almost all of the conventional library support that would be obtained with processor languages such as C and C++. That means developers are stuck on an island where they often are left to their own devices, and even implementing common signal processing algorithms is an expensive and time-consuming proposition. Changing and maintaining this code is also difficult and algorithms are often designed to be specific to the FPGA model in use.

Still, even with these deficiencies the benefits far outweigh the downsides. Software-defined radios exploded in popularity, becoming commonplace and even the default in many domains. This architecture of a digitally-defined radio is now everywhere and has reshaped the way that RF devices perform in the modern world.

“A blank canvas of logic gates—a fabric of logic and routing that could be programmed after manufacturing to perform any desired digital function." - Ross Freeman

With this proliferation, the technology has continued to grow. Recent advances in conventional processors such as GPUs have emerged as an alternative to FPGA-driven designs, allowing developers to leverage the flexibility of processing on instruction-based devices at the cost of greater computational cost and lower determinism. It will be interesting to see where the technology continues to go over the coming years and what breakthroughs will challenge the current paradigm of FPGA-based split frontend and backend design.

jmont

A software engineer with a passion for computer science and software-defined radio.

Related Posts

March 29, 2026

Vitality, header-only VITA 49 for C++

Anyone who has spent time in the world of software-defined radio knows that…

March 23, 2026

Ollama-hpp, header-only language models in C++

The democratization of open-weight, locally-run language models has been one of…

March 21, 2026

Language Models and Artificial Intelligence

"Gradient descent can do it." These were the words of Sam Altman following the…